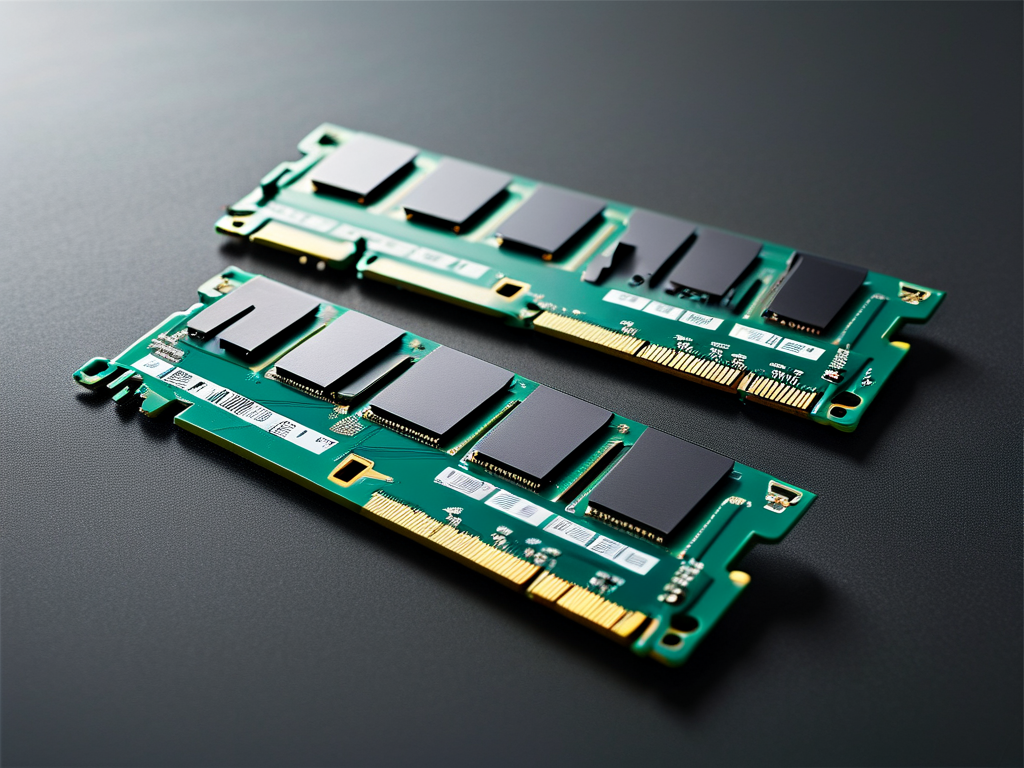

In the realm of computer hardware, DDR (Double Data Rate) memory remains a cornerstone of system performance. Calculating its speed, however, involves more than glancing at product labels like "DDR4-3200" or "DDR5-4800." This article demystifies the technical nuances behind DDR memory speed computation and explains how these metrics translate to real-world computing efficiency.

The Fundamentals of DDR Speed

DDR memory derives its name from its ability to transfer data twice per clock cycle—once on the rising edge and once on the falling edge. This doubles the effective data rate compared to older SDRAM. The base equation for calculating DDR speed starts with the memory’s clock frequency. For example, a DDR4 module labeled "3200" operates at a base clock of 1,600 MHz. By leveraging double data rate technology, the effective transfer rate becomes 3,200 MT/s (megatransfers per second). This relationship is encapsulated in the formula:

Effective Speed = Base Clock Frequency × 2 Generational Differences Matter

Each DDR generation introduces multipliers that affect speed calculations. DDR2 uses a 4x prefetch buffer, DDR3 an 8x buffer, and DDR4/DDR5 employ 16x and 32x buffers, respectively. These buffers allow more data to be processed per cycle, but they don’t directly alter the base clock. Instead, they enhance efficiency through parallel data handling. For instance, a DDR5-4800 module might have a base clock of 1,200 MHz, but its 32n prefetch architecture and dual 32-bit channels amplify throughput beyond simple frequency metrics.

Timing Parameters: The Hidden Variables

While transfer rates dominate marketing materials, timing parameters like CAS latency (CL) profoundly influence real-world performance. A module with CL16 at 3,200 MT/s may deliver comparable responsiveness to a CL18 module at 3,600 MT/s. The formula for calculating actual latency in nanoseconds is:

Latency (ns) = (CAS Latency ÷ Clock Frequency) × 1,000 Using this, a DDR4-3200 (CL16) module yields:

(16 ÷ 1,600 MHz) × 1,000 = 10 ns Channel Configuration and Bandwidth

Modern systems often use dual- or quad-channel memory configurations to multiply bandwidth. Total bandwidth is calculated as:

Bandwidth = (Transfer Rate × Bus Width × Channels) ÷ 8 For a dual-channel DDR4-3200 setup (64-bit bus per channel):

(3,200 MT/s × 64 bits × 2) ÷ 8 = 51.2 GB/s Practical Implications for Users

When selecting RAM, balance speed, latency, and capacity. Gamers might prioritize lower latency (e.g., CL14 DDR4-3200) for faster frame rendering, while video editors could favor higher bandwidth (e.g., DDR5-6000) for smoother 4K workflow. Overclockers should note that pushing frequencies beyond spec often requires adjusting voltages and timings, potentially voiding warranties.

The Future of DDR Speed Metrics

With DDR5 pushing transfer rates beyond 8,000 MT/s and innovations like on-die ECC, understanding speed calculations will grow more complex. Emerging technologies such as 3D-stacked memory and hybrid DDR-LPDDR designs may redefine how performance metrics are quantified.

In , DDR memory speed isn’t just a number—it’s a interplay of clock cycles, prefetch algorithms, latency tolerances, and channel scalability. By mastering these calculations, users can optimize systems for specific workloads and avoid overspending on unnecessary specs.