The memory capacity of 32-bit computer systems has been a fundamental topic in computing history. While modern devices predominantly use 64-bit architectures, understanding the 32-bit memory model remains crucial for maintaining legacy systems and grasping foundational computing concepts. This article explores the technical basis of 32-bit memory addressing, practical implementation challenges, and real-world implications for software development.

At its core, a 32-bit system refers to the width of memory addresses the processor can handle. Each memory address in such systems is represented by a 32-bit binary number, allowing access to 2^32 unique memory locations. Simple arithmetic reveals:

2^32 = 4,294,967,296 addressable bytes

4,294,967,296 bytes ÷ 1024³ = 4 gigabytes (GiB)This calculation shows the theoretical maximum of 4GB addressable memory. However, actual usable memory often falls short due to hardware reservations and memory-mapped I/O operations. For instance, graphics cards and BIOS firmware typically claim portions of this address space, leaving approximately 3-3.5GB available for general-purpose computing in most implementations.

The memory limitation stems from the physical address bus structure. Early x86 processors like the Intel 80386 introduced 32-bit protected mode in 1985, establishing the 4GB ceiling that remained standard for nearly two decades. Engineers later developed Physical Address Extension (PAE) technology to bypass this restriction, enabling 36-bit addressing (up to 64GB) on certain 32-bit processors. However, PAE implementation required specialized OS support and introduced compatibility challenges with legacy software.

Operating system design significantly impacts memory utilization. Microsoft Windows XP (32-bit edition) imposed a 4GB system-wide limit, while server variants like Windows Server 2003 Enterprise Edition supported PAE for up to 64GB through Address Windowing Extensions. Linux distributions adopted PAE support earlier, with kernel versions 2.3.23+ (released 1999) enabling access to up to 64GB physical memory through modified page table structures.

Application developers face unique constraints when targeting 32-bit environments. Individual processes are typically limited to 2GB of virtual address space in standard configurations, expandable to 3GB through /3GB boot switches in Windows or similar kernel parameters in Linux. This restriction impacts memory-intensive applications like video editing software or scientific simulations, often requiring specialized memory management techniques such as:

- Memory-mapped file I/O

- Custom memory pooling implementations

- Process-level memory segmentation

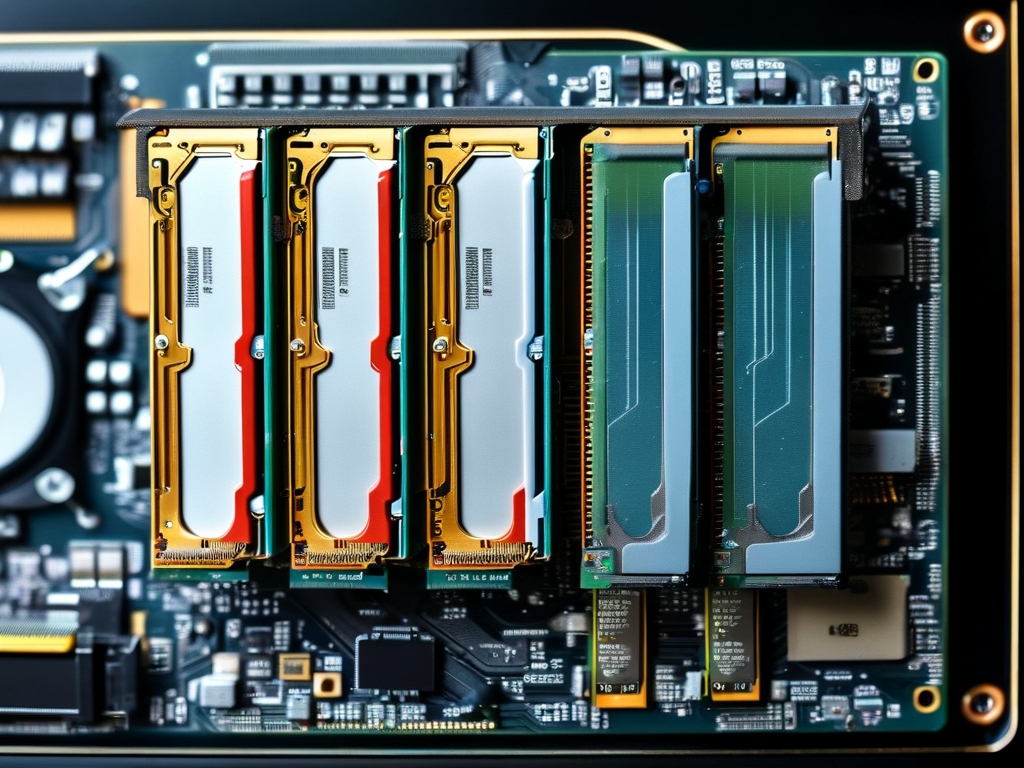

Hardware manufacturers developed various workarounds before the industry transitioned to 64-bit computing. Graphics cards began incorporating dedicated video memory (VRAM) to reduce system memory consumption, while motherboard designs implemented memory remapping features in BIOS settings. These partial solutions extended the lifespan of 32-bit systems but couldn't match the exponential growth in software memory demands.

The transition to 64-bit architectures resolved these limitations by expanding addressable memory to 16 exabytes (2^64 bytes). Modern systems typically implement 48-bit physical addressing (256TB) as a practical balance between capacity and implementation complexity. However, 32-bit systems persist in embedded devices, IoT applications, and legacy industrial controls where 4GB proves sufficient and architectural simplicity remains advantageous.

For developers maintaining 32-bit software, memory optimization remains critical. Techniques include:

// Example of memory-efficient structure packing

#pragma pack(push, 1)

typedef struct {

uint16_t sensorID;

uint32_t timestamp;

int8_t status;

} SensorData;

#pragma pack(pop)This code demonstrates structure packing to minimize memory padding in C/C++ applications. Such optimizations become essential when working close to the 4GB boundary.

In , while 32-bit systems impose a 4GB memory ceiling, understanding this limitation provides valuable insights into computer architecture evolution. The constraint drove innovations in memory management techniques and hardware design, ultimately paving the way for modern 64-bit computing. As technology continues advancing, the lessons learned from 32-bit memory limitations remain relevant for optimizing resource usage across all computing platforms.