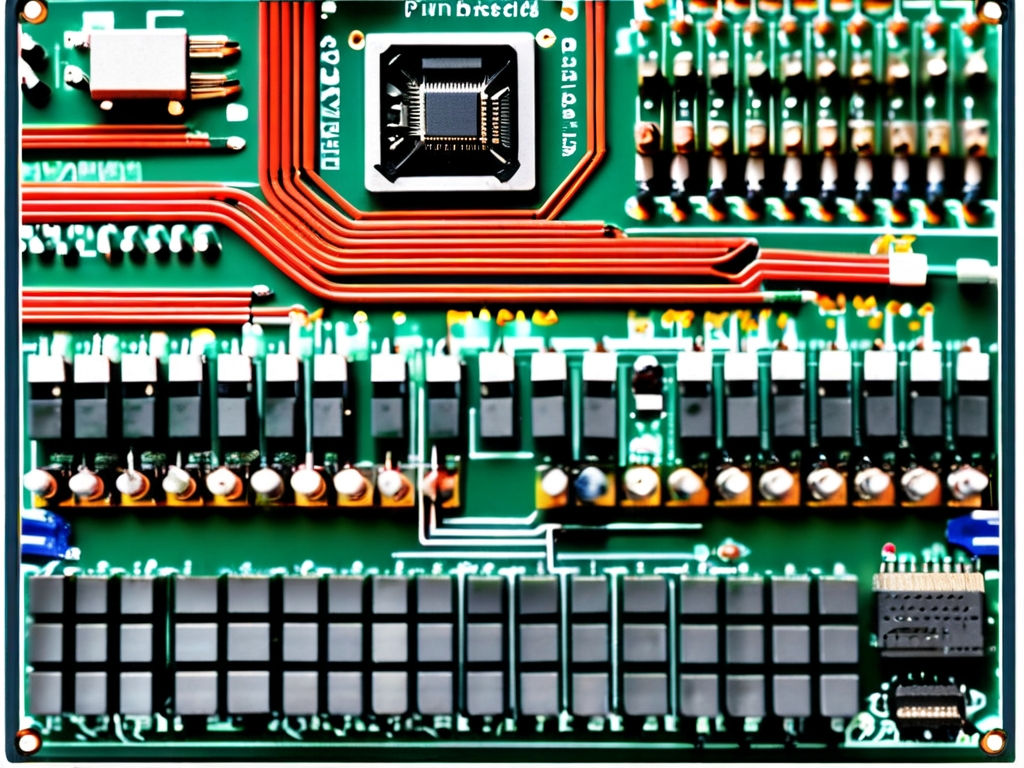

Designing a printed circuit board (PCB) begins with creating a schematic diagram, which serves as the blueprint for the electrical connections between components. However, before moving to the layout phase, it is critical to compile and check the schematic thoroughly to avoid costly errors. This article provides a detailed guide on how to compile and inspect a PCB schematic effectively.

1. Understanding Schematic Compilation

Schematic compilation is the process of converting a human-readable schematic diagram into a machine-interpretable format. This step ensures that the design adheres to predefined electrical and logical rules. Most PCB design software, such as Altium Designer, KiCad, or OrCAD, includes built-in compilation tools to automate this process. During compilation, the software checks for inconsistencies, such as unconnected pins, duplicate component identifiers, or mismatched footprints.

2. Preparing for Compilation

Before compiling, ensure the schematic is organized:

- Component Libraries: Verify that all components are linked to correct symbols and footprints. Missing or mismatched libraries can cause errors during compilation.

- Net Labels: Ensure all nets (electrical connections) are properly labeled. Unlabeled nets may lead to unintended shorts or open circuits.

- Hierarchical Sheets: If using multi-sheet designs, confirm that inter-sheet connections (e.g., ports and off-sheet connectors) are correctly mapped.

3. Running the Compilation Process

In most tools, compilation is initiated via a menu command (e.g., Project > Compile in Altium). The software will generate a report highlighting warnings and errors. Common issues include:

- Unconnected Pins: Pins left floating without a net connection.

- Duplicate Designators: Two components sharing the same reference identifier (e.g., two resistors labeled R1).

- Power Supply Conflicts: Incorrect voltage levels or conflicting power net assignments.

Address these errors systematically before proceeding.

4. Electrical Rule Checking (ERC)

ERC is a subset of compilation focused on electrical integrity. It flags issues like:

- Floating Inputs: Unconnected input pins that may cause undefined logic states.

- Driver Conflicts: Multiple outputs driving the same net (e.g., two ICs trying to control a single line).

- Power-Ground Shorts: Accidental direct connections between power and ground nets.

Configure ERC settings to match your design requirements. For example, some unconnected pins (e.g., test points) may be intentionally left open and should be exempted from errors.

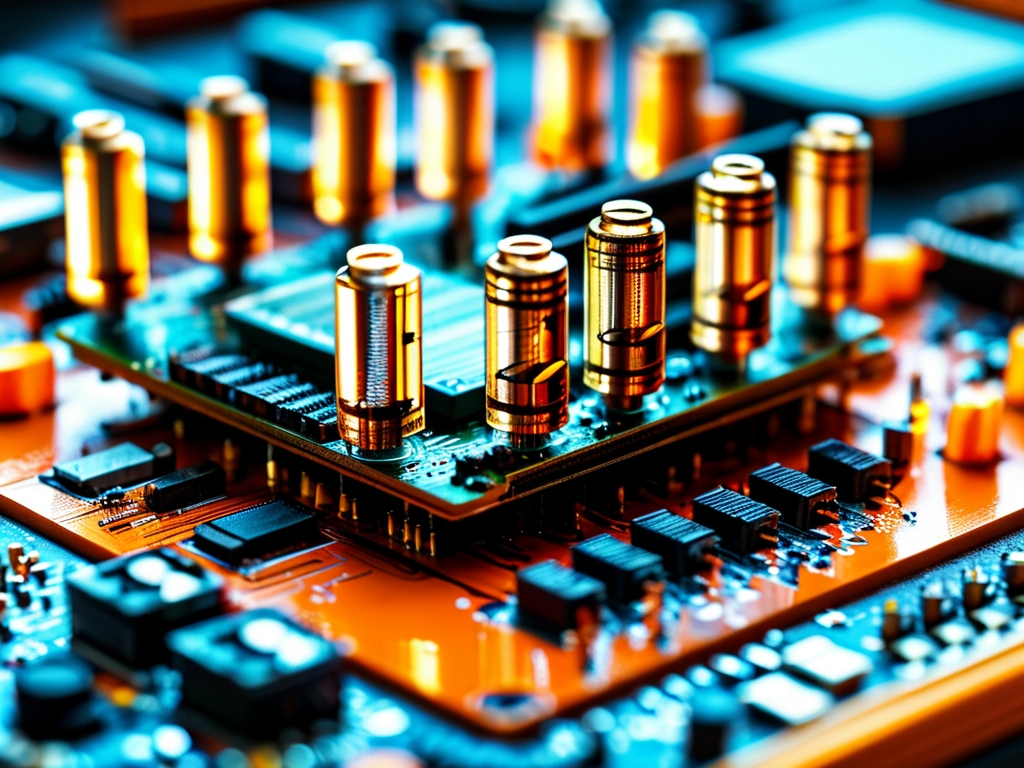

5. Cross-Probing with Layout Tools

After compiling the schematic, cross-probe it with the PCB layout tool to ensure consistency. This step helps identify discrepancies, such as missing components or incorrect net assignments. Modern tools allow bidirectional synchronization, enabling real-time updates between the schematic and layout.

6. Manual Inspection

Automated checks are indispensable, but manual review remains crucial. Focus on:

- Component Values: Verify resistor, capacitor, and IC values against the bill of materials (BOM).

- Signal Flow: Ensure logical signal paths match the intended functionality (e.g., microcontroller pins correctly routed to peripherals).

- Annotations: Confirm all components are labeled, and text is legible.

7. Design Review with Stakeholders

Collaborate with team members or clients to review the schematic. Fresh eyes can catch overlooked issues, such as incorrect part substitutions or missing decoupling capacitors. Use annotation tools to mark up the schematic during discussions.

8. Simulation and Validation

For complex designs, run simulations (e.g., SPICE for analog circuits) to validate performance. Simulations can reveal issues like signal integrity problems, excessive power dissipation, or timing mismatches that static checks might miss.

9. Version Control and Documentation

After finalizing the schematic:

- Save Revisions: Use version control software to track changes.

- Generate Reports: Export netlists, BOMs, and ERC reports for future reference.

- Archive Files: Store schematics, libraries, and notes in a secure location.

10. Common Pitfalls and Solutions

- Silent Errors: Some tools may not flag certain issues (e.g., incorrect resistor values). Mitigate this by cross-referencing the BOM.

- Overlooked Design Rules: Ensure ERC settings align with project specifications (e.g., high-voltage isolation requirements).

- Footprint Mismatches: Double-check pad sizes and spacings, especially for components like QFPs or BGAs.

Compiling and checking a PCB schematic is a meticulous but essential process. By combining automated tools, manual reviews, and collaborative feedback, designers can eliminate errors early, reducing the risk of board respins and project delays. A well-verified schematic lays the foundation for a reliable PCB layout, ensuring the final product performs as intended.