The semiconductor embedded development workflow represents a sophisticated convergence of hardware engineering and software optimization. This multi-stage process requires meticulous planning across architecture design, code implementation, and system validation. Unlike generic software development, embedded systems in semiconductors demand precise coordination between silicon characteristics and program execution.

At the core of this workflow lies the requirement analysis phase. Engineers must first define operational parameters such as power consumption thresholds, clock speeds, and memory constraints. For automotive microcontrollers, this might involve calculating worst-case scenario current draws below 15mA while maintaining real-time response capabilities. These specifications directly influence subsequent design decisions, creating a ripple effect throughout the development cycle.

Hardware-software co-design emerges as a critical differentiator in semiconductor projects. Design teams employ electronic design automation (EDA) tools like Cadence Virtuoso to model circuit behaviors while simultaneously developing firmware prototypes. A typical implementation might involve creating Verilog HDL models for digital signal processing blocks alongside C-language drivers for peripheral interfaces. This parallel development approach reduces iteration cycles but requires strict version control through platforms like Git, with branching strategies tailored for mixed hardware-description-language and software codebases.

The integration phase presents unique challenges when physical silicon meets embedded logic. Engineers utilize JTAG debuggers and logic analyzers to validate signal integrity across fabricated chips. For example, debugging I²C communication failures might involve capturing waveform patterns using a Teledyne LeCroy oscilloscope while cross-referencing register values through OpenOCD interfaces. Power analysis tools such as Keysight's N6705C help identify current leakage points in sleep modes, often revealing optimization opportunities that save microamps – critical for battery-operated devices.

Automated testing frameworks form the backbone of quality assurance. Continuous integration pipelines execute regression tests on FPGA emulators, checking for both functional correctness and timing constraints. A robotics controller chip might undergo 10,000+ test cycles simulating motor PWM variations under different temperature profiles. Python scripts frequently automate these test sequences, integrating with industry-standard tools like Jenkins to generate compliance reports meeting ISO 26262 automotive safety standards.

Three critical best practices distinguish successful semiconductor embedded projects:

- Implementing traceability matrices linking requirements to test cases

- Maintaining thermal simulation data throughout the design process

- Adopting secure boot mechanisms during firmware deployment

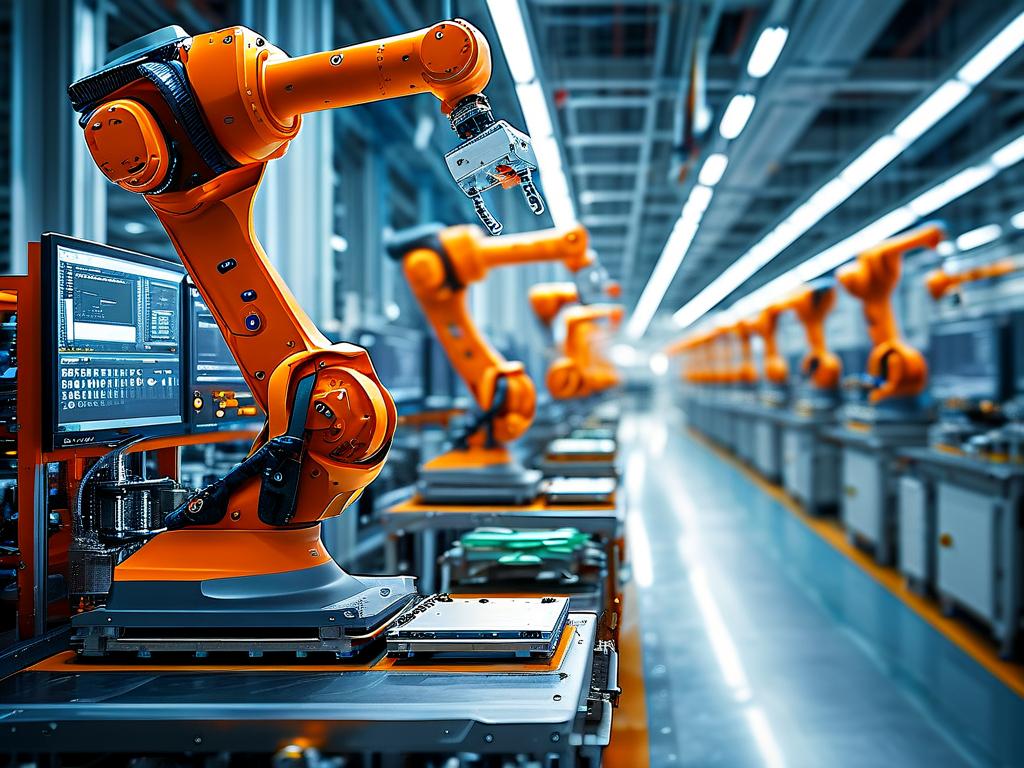

Real-world deployments often reveal unexpected environmental factors. A recent industrial IoT sensor project demonstrated this when electromagnetic interference (EMI) from factory equipment caused memory bit-flips. The solution involved modifying both hardware layout (adding guard rings around SRAM cells) and software (implementing ECC memory checks), highlighting the interdependent nature of semiconductor embedded systems.

Looking forward, the integration of machine learning accelerators into embedded architectures introduces new workflow complexities. Design teams must now account for neural network quantization parameters during RTL design while optimizing inference engines for specific instruction sets. Tools like TensorFlow Lite Micro are becoming essential in bridging AI models with resource-constrained embedded targets, creating fresh challenges in memory allocation and computational latency management.

The evolution of RISC-V architectures further transforms development paradigms. Open-source processor cores enable custom instruction extensions, allowing engineers to tailor chips for specific embedded workloads. A smart agriculture controller might incorporate custom SHA-256 encryption instructions while eliminating unused floating-point units, achieving both security enhancements and silicon area reduction.

In , semiconductor embedded development demands a holistic approach blending electrical engineering precision with software development agility. As IoT and edge computing drive demand for specialized chips, mastering this workflow becomes pivotal for delivering efficient, reliable embedded solutions. Teams that successfully integrate cross-domain expertise while leveraging advanced verification methodologies will lead innovation in this critical field.