Understanding the number of chips embedded in a memory stick is a critical aspect of evaluating its performance and compatibility with computing systems. This article explores the factors influencing chip count, calculation methodologies, and practical implications for users and manufacturers.

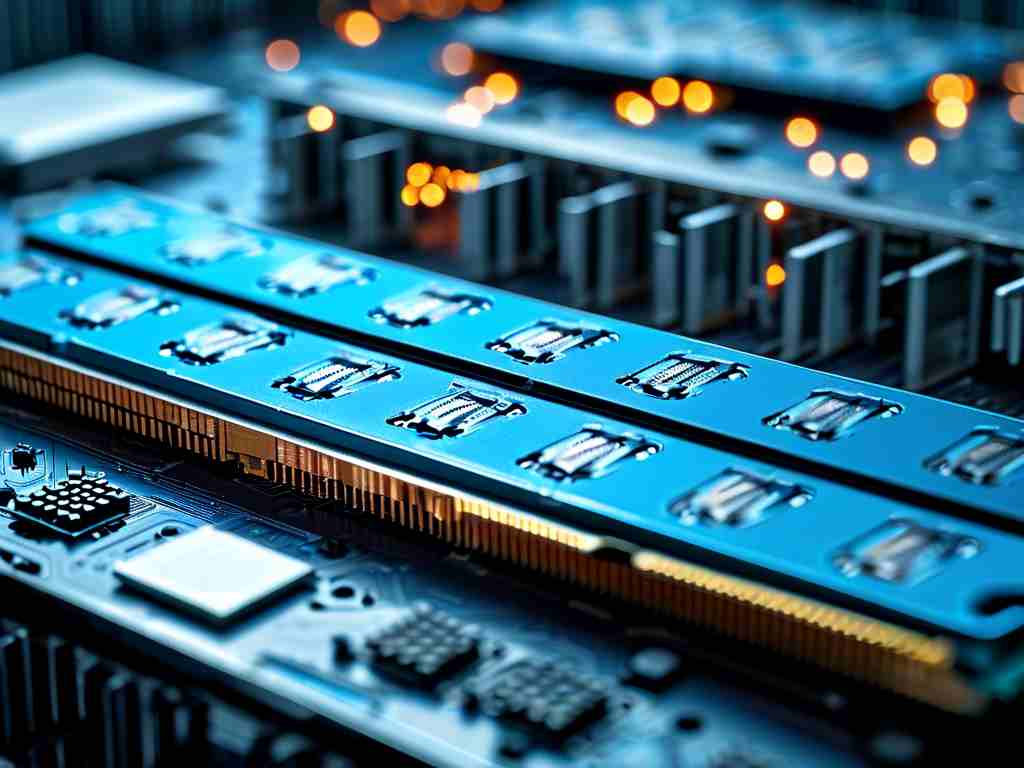

Fundamentals of Memory Stick Architecture

A memory stick, or RAM module, comprises multiple integrated circuits (ICs) or chips responsible for data storage and retrieval. These chips are mounted on a printed circuit board (PCB) and work in tandem to deliver the module’s total capacity. The relationship between chip count and capacity depends on the density of individual chips and the module’s design specifications. For example, a 16GB DDR4 module might use sixteen 1GB chips or eight 2GB chips, depending on the manufacturer’s design choices.

Chip Count Calculation Formula

The formula for determining the number of chips in a memory stick is:

Number of Chips = (Total Module Capacity) / (Individual Chip Capacity) This equation assumes uniform chip capacities. However, variations occur when manufacturers combine chips of different densities to meet specific performance or cost requirements. For instance, a 32GB module might integrate two 8GB chips and four 4GB chips, totaling six chips.

Role of Data Bus and Channel Configuration

Memory modules must align with a system’s data bus width, which directly impacts chip count. A standard 64-bit DDR4 module requires eight 8-bit chips to match the bus width. If a chip has a 16-bit interface, only four chips would be needed. This principle explains why high-performance modules often feature more chips with lower bit-width configurations to optimize data transfer rates.

Error-Correcting Code (ECC) Considerations

ECC memory modules include additional chips for error detection and correction. A typical ECC DDR4 module with 72-bit bus width (64 data bits + 8 ECC bits) requires nine 8-bit chips instead of eight. This redundancy ensures data integrity but increases chip count and power consumption.

Technological Advancements and Chip Density

Advancements in semiconductor manufacturing have enabled higher-density chips, reducing the physical number of chips per module. A modern 64GB DDR5 module might use four 16GB chips, whereas older DDR3 technology would require sixteen 4GB chips for the same capacity. 3D-stacking technology further amplifies this trend by vertically layering memory cells within a single chip package.

Practical Examples and Industry Variations

- A consumer-grade 8GB DDR4 module with eight 1GB chips (64-bit bus).

- A server-grade 32GB DDR4 ECC module with nine 4GB chips (72-bit bus).

- A compact 16GB LPDDR5 module with four 4GB chips using 3D stacking.

These examples highlight how application-specific requirements—such as space constraints, power efficiency, or error tolerance—drive chip count decisions.

Manufacturing Trade-offs and Cost Dynamics

Higher chip counts increase production complexity and PCB real estate usage but offer redundancy and repair flexibility. Conversely, fewer high-density chips reduce material costs but heighten the risk of module failure due to single-point defects. Manufacturers balance these factors based on target markets—budget consumer modules prioritize cost reduction, while enterprise-grade products emphasize reliability.

Future Trends in Memory Module Design

Emerging technologies like hybrid bonding and chiplet architectures are reshaping chip count paradigms. For example, AMD’s Zen 4 processors utilize vertically stacked cache chips alongside traditional memory modules, blending different chip types for optimized performance. Such innovations suggest that future "chip counts" may refer to heterogeneous collections of specialized ICs rather than uniform memory cells.

Calculating the number of chips in a memory stick involves analyzing capacity, bus width, error-correction needs, and technological constraints. As chip densities continue to grow and architectures evolve, users must prioritize compatibility and use-case requirements over raw chip counts when selecting memory solutions.