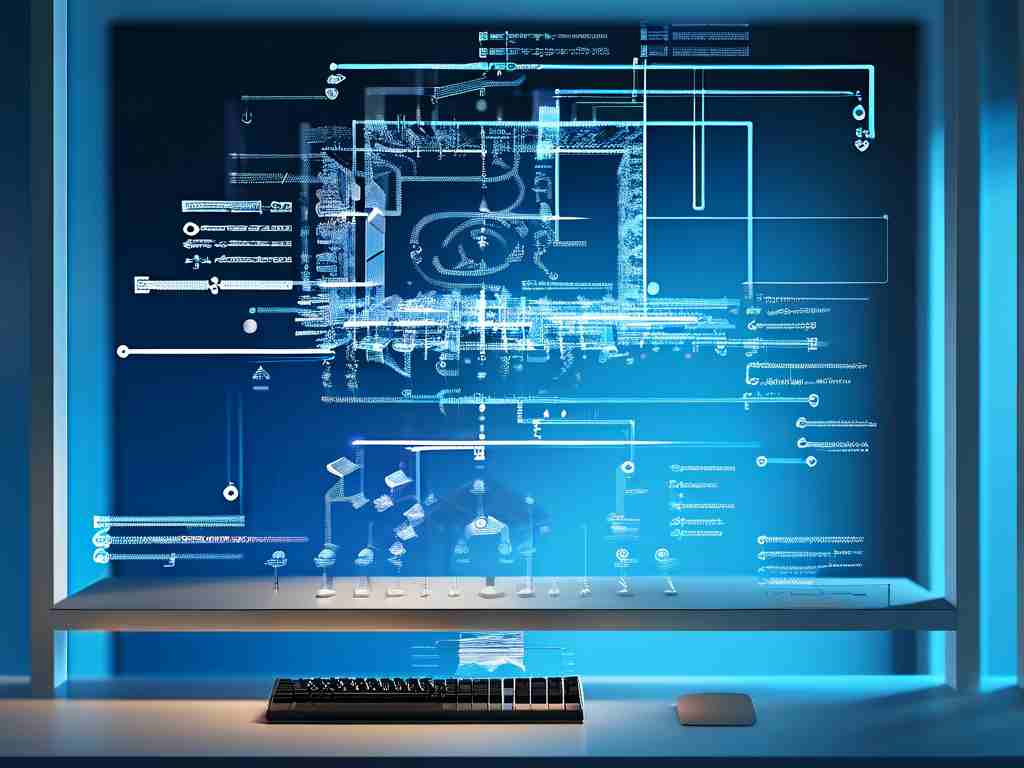

In the realm of programming language implementation, the compiler backend serves as the critical bridge between abstract source code and executable machine instructions. While frontend components like lexical analysis and syntax parsing often receive more attention, the backend's role in transforming intermediate representations into efficient low-level code remains pivotal. This article explores the architecture, processes, and technical challenges of modern compiler backends.

Intermediate Code Generation

The backend's journey begins with intermediate representation (IR) – a platform-agnostic code structure generated by the frontend. This stage typically converts abstract syntax trees into three-address code or static single assignment (SSA) form. For example:

// Original expression x = (a + b) * (c - d); // Three-address code t1 = a + b t2 = c - d x = t1 * t2

This standardized format enables subsequent optimizations while preserving program semantics. Modern compilers like LLVM employ sophisticated IR systems that maintain metadata for debugging and analysis.

Optimization Strategies

Machine-independent optimizations form the backbone of backend processing:

- Constant Propagation: Replacing variables with known constant values

- Dead Code Elimination: Removing unreachable instructions

- Loop Unrolling: Expanding iterative structures for pipeline efficiency

Consider this optimization sequence:

; Original LLVM IR %sum = add i32 %a, 7 %result = mul i32 %sum, 0 ; After optimization %result = 0

The backend intelligently simplifies expressions through mathematical identity recognition.

Target Code Generation

The final translation phase adapts optimized IR to specific hardware architectures. This involves three critical subphases:

Instruction Selection

Pattern matching algorithms map IR operations to machine instructions. For x86 architectures:

; IR: %r = add i32 %a, %b lea eax, [ecx + edx]

Modern compilers use declarative instruction descriptions through tools like LLVM's TableGen.

Register Allocation

This NP-hard problem determines optimal register usage through graph coloring algorithms. A typical interference graph helps prevent register conflicts:

Variables: {a, b, c}

Edges: a-b, a-c // Cannot share registers Instruction Scheduling

Reordering operations to maximize pipeline utilization:

; Before scheduling LOAD R1, [mem1] ADD R2, R1, #5 LOAD R3, [mem2] ; After scheduling LOAD R1, [mem1] LOAD R3, [mem2] ADD R2, R1, #5

Machine-Specific Optimizations

Backends implement architecture-dependent enhancements:

- SIMD Vectorization for modern CPUs

- Branch Prediction Hints in embedded systems

- Power-Aware Scheduling for mobile devices

An ARM Cortex-M example demonstrates thumb instruction selection:

; Instead of 32-bit instructions add r0, r1 ; Use 16-bit Thumb equivalent adds r0, r1

Symbol Table Management

The backend maintains critical semantic information through symbol tables that track:

- Variable data types

- Memory offsets

- Scope hierarchies

- Debugging metadata

Error Handling

While primarily frontend responsibility, backends detect:

- Architecture-specific overflows

- Hardware resource limitations

- ABI compliance issues

Challenges in Modern Systems

Emerging technologies present new backend design considerations:

- Heterogeneous Computing: Coordinating CPU/GPU/TPU code generation

- JIT Compilation: Runtime optimizations based on execution profiles

- Security Enhancements: Implementing pointer authentication (e.g., ARMv8.3)

The compiler backend represents a sophisticated blend of theoretical computer science and practical engineering. From register allocation algorithms to machine-specific peephole optimizations, these components ensure software efficiently utilizes modern hardware capabilities. As computing architectures evolve, backend developers continue pushing the boundaries of code generation efficiency and adaptability.